# MOTOROLA SEMICONDUCTOR TECHNICAL DATA

# MC68HC11EA9 MC68HC711EA9

# Technical Summary 8-Bit Microcontrollers

### **1** Introduction

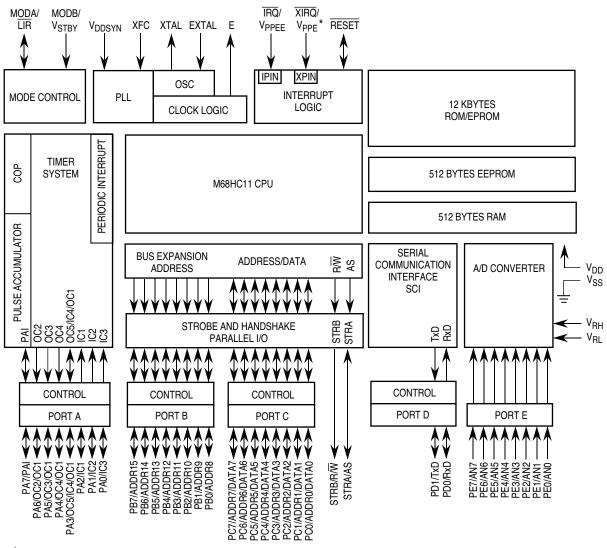

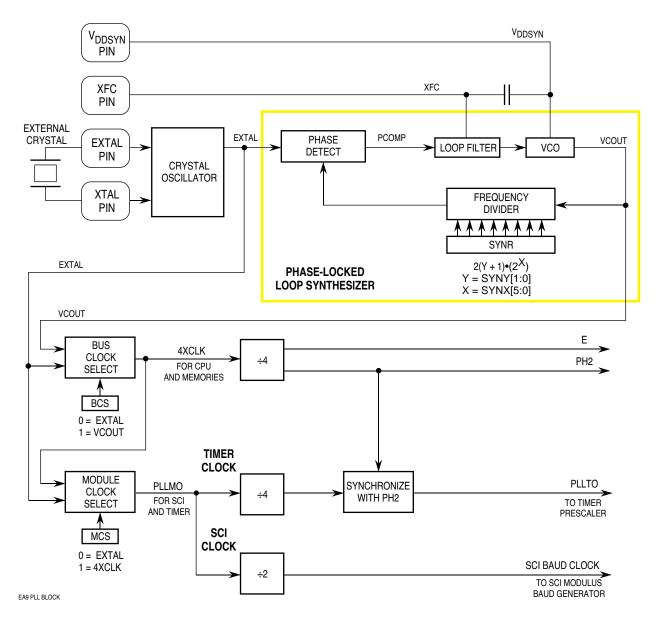

The MC68HC11EA9 and MC68HC711EA9 microcontroller units (MCUs) are high-performance members of the M68HC11 family of MCUs. The MC68HC(7)11EA9 MCUs have a multiplexed external address and data bus and are characterized by high speed and low power consumption. Their fully static design allows operation at frequencies from 3 MHz to dc. The addition of a phase-locked loop (PLL) frequency synthesizer to the timer circuitry further enhances low-power operation and allows the use of lower frequency crystals while maintaining a clock speed of up to 3 MHz.

This document contains information concerning standard and custom-ROM devices. Standard devices are those with ROM or with EPROM replacing ROM (MC68HC711EA9). Custom-ROM devices have a ROM array that is programmed at the factory to customer specifications. Where information in this document refers to both the ROM and EPROM versions, the device is referred to as MC68HC(7)11EA9.

#### 1.1 Features

- M68HC11 CPU

- 512 Bytes RAM (Data Retained During Standby, by use of V<sub>STBY</sub>)

- 12 Kbytes Mask-Programmed ROM or EPROM

- 512 Bytes Electrically Erasable Programmable ROM (EEPROM)

- PROG Mode Allows Use of Standard EPROM Programmer (27C256 Footprint)

- Multiplexed Address and Data Buses Reduce Pin Count

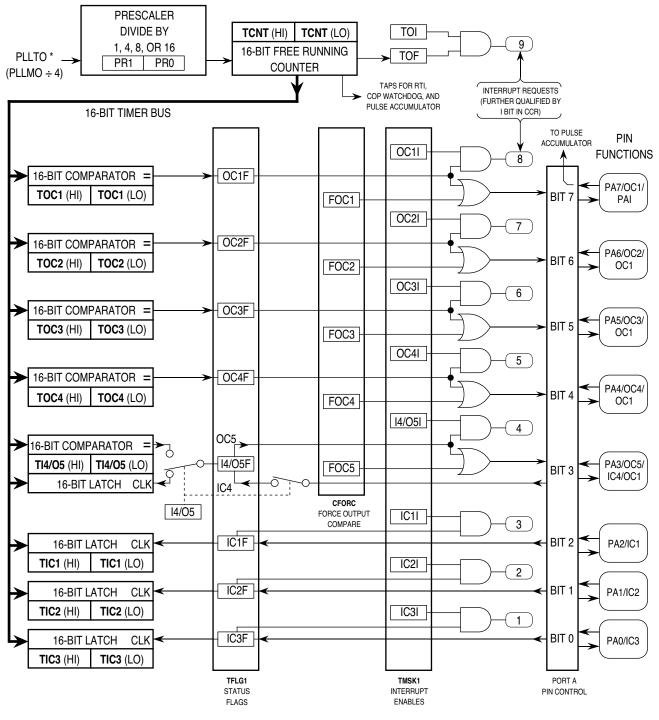

- Enhanced 16-Bit Timer with Four-Stage Programmable Prescaler

- Three Input Capture (IC) Channels

- Four Output Compare (OC) Channels

- One Additional Channel, Selectable as Fourth IC or Fifth OC

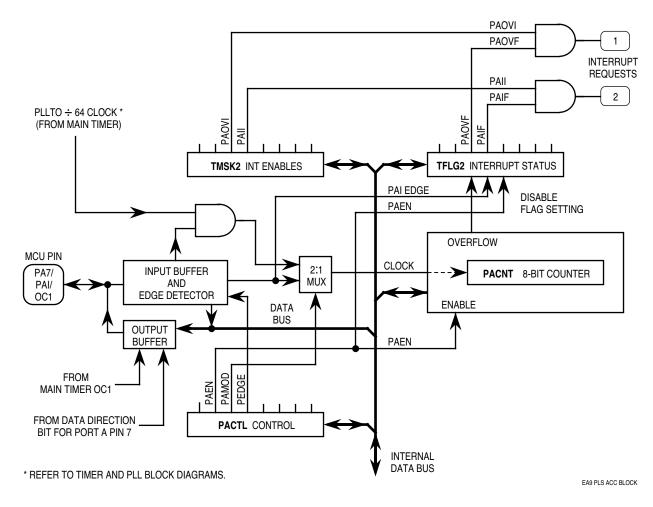

- 8-Bit Pulse Accumulator

- Phase-Locked Loop (PLL) Frequency Synthesizer for Reduced Power Consumption

- Power Saving STOP and WAIT Modes

- Real-Time Interrupt Circuit

- Computer Operating Properly (COP) Watchdog Timer

- Clock Monitor Circuit

- Enhanced Asynchronous Nonreturn to Zero (NRZ) Serial Communications Interface (SCI)

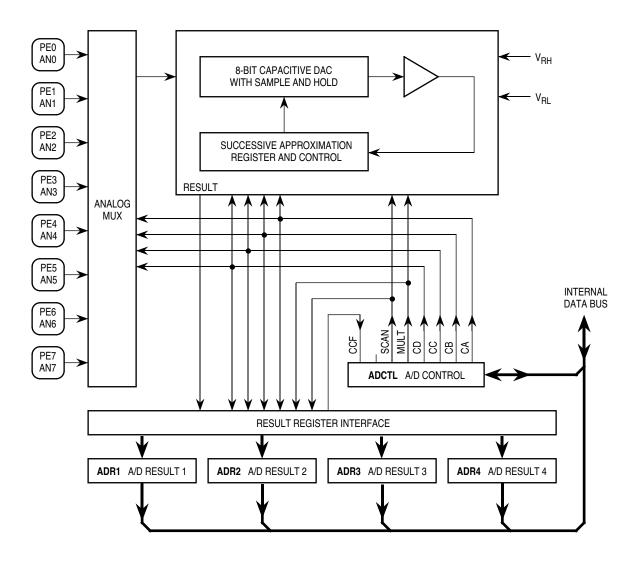

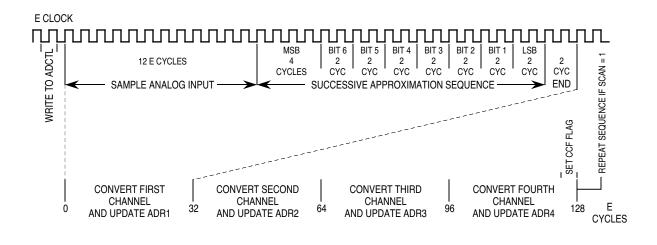

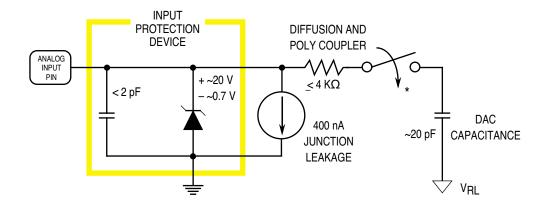

- Eight-Channel 8-Bit Analog-to-Digital (A/D) Converter

- Five Input/Output (I/O) Ports (34 Pins)

- Four Bidirectional I/O Ports (26 Pins)

- One Fixed Input-Only Port (8 Pins)

- Two Alternate, Fixed Input-Only Pins (XIRQ pin/XPIN bit and IRQ pin/IPIN bit)

- Available in 52-Pin Plastic Leaded Chip Carrier (PLCC), 52-Pin Windowed Ceramic Leaded Chip Carrier (CLCC), and 56-Pin SDIP (0.070" Lead Spacing)

This document contains information on a new product. Specifications and information herein are subject to change without notice.

# **TABLE OF CONTENTS**

| Se | ection       |                                                 | Page |

|----|--------------|-------------------------------------------------|------|

| 1  |              | Introduction                                    | 1    |

| •  | 1.1          | Features                                        | •    |

| 2  |              | Device Package Options and Ordering Information | 5    |

| -  | 2.1          | Available Device Packages                       | -    |

|    | 2.2          | Ordering Information                            |      |

| 3  |              | Central Processing Unit                         | 8    |

| J  | 3.1          | Programming Model                               |      |

|    | 3.2          | CPU Registers                                   |      |

|    | 3.2.1        | Accumulators A, B, and D                        |      |

|    | 3.2.2        | Index Register X (IX)                           |      |

|    | 3.2.3        | Index Register Y (IY)                           |      |

|    | 3.2.4        | Stack Pointer (SP)                              |      |

|    | 3.2.5        | Program Counter (PC)                            |      |

|    | 3.2.6        | Condition Code Register (CCR)                   | 9    |

|    | 3.2.7        | Addressing Modes                                | 9    |

| 4  |              | Operating Modes and On-Chip Memory              | 10   |

| -  | 4.1          | Single-Chip Mode                                |      |

|    | 4.2          | Expanded Mode                                   |      |

|    | 4.3          | Test Mode                                       |      |

|    | 4.4          | Bootstrap Mode                                  |      |

|    | 4.5          | Mode Selection                                  | 11   |

|    | 4.6          | RAM                                             |      |

|    | 4.7          | Bootstrap ROM                                   |      |

|    | 4.8          | Memory Map and Register Block                   |      |

|    | 4.9<br>4.9.1 | ROM/EPROM/OTPROM<br>EPROM Emulation Mode        |      |

|    | 4.9.1        | Programming an Individual EPROM Address         |      |

|    | 4.9.2        | Programming EPROM with Downloaded Data          |      |

|    | 4.10         | EEPROM                                          |      |

|    | 4.10.1       | Programming and Erasing EEPROM                  |      |

|    | 4.10.2       |                                                 |      |

|    | 4.10.3       | •                                               |      |

| 5  |              | Resets and Interrupts                           | 22   |

|    |              | •                                               |      |

| 6  |              | Parallel Input/Output                           | 26   |

| 7  |              | Timing System                                   | 31   |

|    | 7.1          | Phase-Locked Loop Synthesizer                   |      |

|    | 7.2          | Main Timer                                      |      |

|    | 7.3          | Real-Time Interrupt                             |      |

| ~  | 7.4          | Pulse Accumulator                               |      |

| 8  |              | Serial Communications Interface                 | 47   |

| 9  |              | Analog-to-Digital Converter                     | 54   |

# **Register Index**

|           | A/D Control/Status                             | ¢4000            |

|-----------|------------------------------------------------|------------------|

|           |                                                | -                |

|           | A/D Results                                    |                  |

|           | EEPROM Block Protect                           |                  |

|           |                                                |                  |

|           | Security, COP, ROM/EPROM/EEPROM Enables        |                  |

|           | Arm/Reset COP Timer Circuitry                  |                  |

|           | Port A Data Direction                          |                  |

|           | Port B Data Direction                          |                  |

|           | Port C Data Direction                          | -                |

| DDRD      | Port D Data Direction                          | -                |

| HPRIO     |                                                |                  |

| INIT      | RAM and I/O Mapping Register                   | .\$103D14        |

| OC1D      | Output Compare 1 Data                          | .\$100D          |

| OC1M      | Output Compare 1 Mask                          | .\$100C          |

| OPTION    | System Configuration Options                   | .\$1039          |

| PACNT     | Pulse Accumulator Counter                      |                  |

|           | Pulse Accumulator Control.                     |                  |

|           | EPROM and EEPROM Programming Control Register. |                  |

|           | Port I/O Control                               |                  |

|           | PLL Control                                    |                  |

|           | Port A Data.                                   |                  |

|           | Port B Data.                                   | -                |

|           | Port C Data                                    |                  |

|           | Port C Latched Data                            |                  |

|           | Port D Data                                    |                  |

|           | Port E Data                                    |                  |

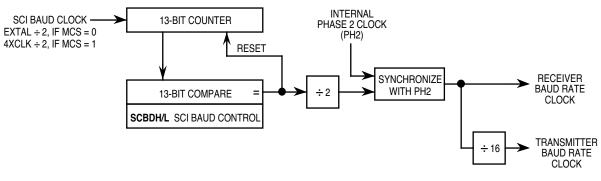

|           | SCI Baud Rate Select High/Low                  |                  |

|           |                                                |                  |

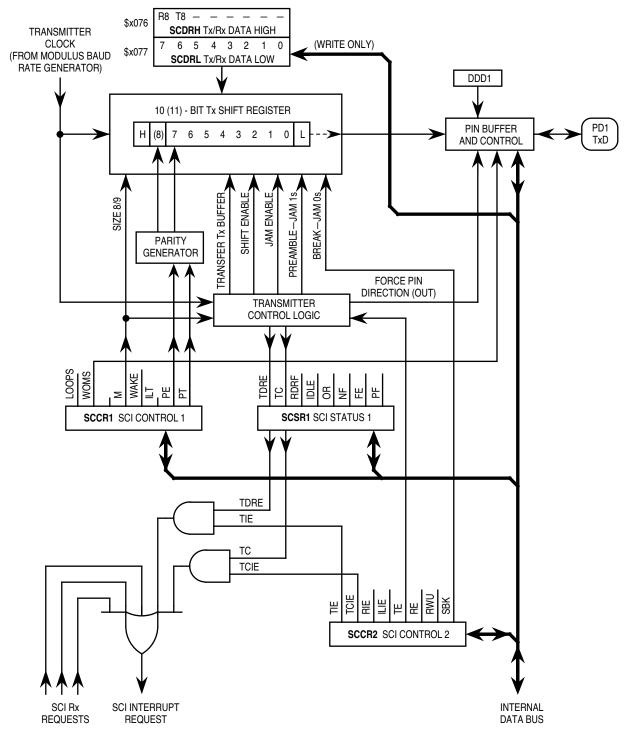

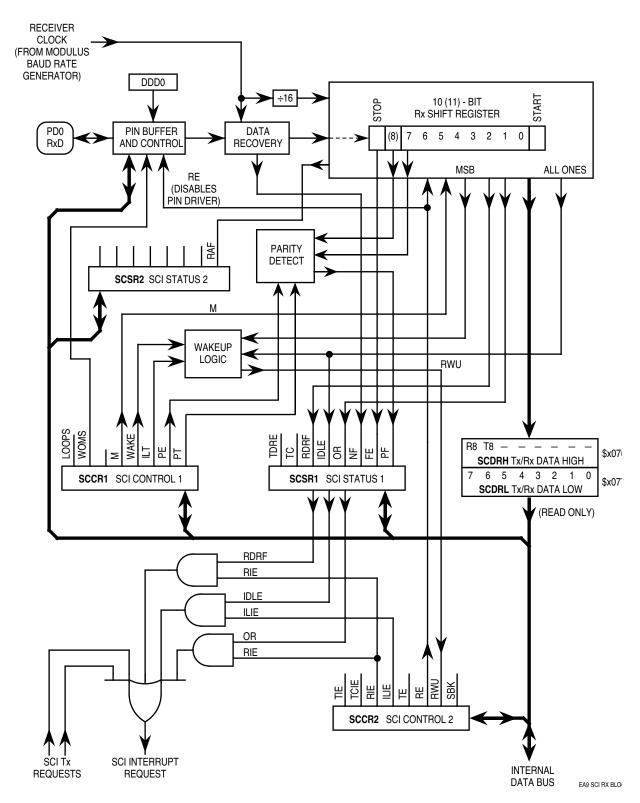

|           | SCI Control Register 1                         |                  |

|           | SCI Control Register 2                         |                  |

|           | SCI Data High, SCI Data Low                    |                  |

|           | SCI Status Register 1                          |                  |

|           | SCI Status Register 2.                         |                  |

|           | Frequency Synthesizer Control                  |                  |

|           | Timer Counter                                  |                  |

|           | Timer Control 1                                |                  |

|           | Timer Control 2                                |                  |

|           | Timer Interrupt Flag 1                         | -                |

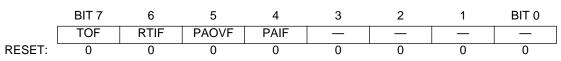

| TFLG2     | Timer Interrupt Flag 2                         | .\$1025          |

| TI4/O5    | Timer Input Capture 4/Output Compare 5         | .\$101E-\$101F42 |

| TIC1–TIC3 | Timer Input Capture                            | .\$1010–\$1015   |

| TMSK1     | Timer Interrupt Mask 1                         | .\$102243        |

|           | Timer Interrupt Mask 2                         |                  |

|           | Timer Output Compare                           |                  |

|           | · ·                                            |                  |

\* V<sub>PPE</sub> APPLIES ONLY TO DEVICES WITH EPROM/OTPROM.

EA9 BLOCK

## 2 Device Package Options and Ordering Information

#### 2.1 Available Device Packages

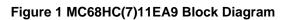

The MC68HC(7)11EA9 MCUs are available in a 52-pin plastic leaded chip carrier (PLCC) and a 52-pin ceramic leaded chip carrier (CLCC). Refer to **Figure 2**. A plastic 56-pin shrink DIP (SDIP) package is also available. Refer to **Figure 3**.

The EPROM-based MC68HC711EA9 is available in a windowed 52-pin ceramic leaded chip carrier (CLCC). A one-time-programmable (OTP) version of the MC68HC711EA9 is available by ordering the device in a non-windowed package. Refer to **Table 1**.

\* V<sub>PPE</sub> APPLIES ONLY TO DEVICES WITH EPROM/OTPROM.

EA9 52-PIN PLCC

#### Figure 2 MC68HC(7)11EA9 PLCC/CLCC Pin Assignments

| V <sub>DD</sub> [         | 1  | $\bigcirc$       | 56□ V <sub>SS</sub> |

|---------------------------|----|------------------|---------------------|

| MODA/LIR                  | 2  |                  | 55 V <sub>RH</sub>  |

| STRA/AS 🗌                 | 3  |                  | 54 V <sub>RL</sub>  |

| E                         | 4  |                  | 53 PE7/AN7          |

| STRB/R/W                  | 5  |                  | 52 PE3/AN3          |

| EXTAL 🗆                   | 6  |                  | 51 PE6/AN6          |

| NC 🗆                      | 7  |                  | 50 PE2/AN2          |

| XTAL 🗌                    | 8  |                  | 49 PE5/AN5          |

| PC0/ADDR0/DATA0           | 9  |                  | 48 PE1/AN1          |

| PC1/ADDR1/DATA1           | 10 |                  | 47 PE4/AN4          |

| PC2/ADDR2/DATA2           | 11 |                  | 46 PE0/AN0          |

| PC3/ADDR3/DATA3           | 12 |                  | 45 PB0/ADDR8        |

| PC4/ADDR4/DATA4           | 13 | MC68HC(7)11EA9   | 44 PB1/ADDR9        |

| PC5/ADDR5/DATA5           | 14 |                  | 43 PB2/ADDR10       |

|                           | 15 | (0.070" SPACING) | 42 PB3/ADDR11       |

| PC7/ADDR7/DATA7           | 16 |                  | 41 PB4/ADDR12       |

| RESET                     | 17 |                  | 40 PB5/ADDR13       |

|                           | 18 |                  | 39 PB6/ADDR14       |

| * XIRQ/V <sub>PPE</sub> [ | 19 |                  | 38 PB7/ADDR15       |

| IRQ/V <sub>PPEE</sub>     | 20 |                  | 37 NC               |

| PD0/RxD                   | 21 |                  | 36 PA0/IC3          |

| V <sub>SS</sub> [         | 22 |                  | 35 PA1/IC2          |

| PD1/TxD                   | 23 |                  | 34 PA2/IC1          |

|                           | 24 |                  | 33 PA3/OC5/IC4/OC1  |

| V <sub>DDSYN</sub> [      | 25 |                  | 32 PA4/OC4/OC1      |

| XFC [                     | 26 |                  | 31 PA5/OC3/OC1      |

| v <sub>SS</sub> □         | 27 |                  | 30 PA6/OC2/OC1      |

| V <sub>DD</sub> [         | 28 |                  | 29 PA7/PAI/OC1      |

|                           |    |                  |                     |

$^{\star}$  V\_{PPE} APPLIES ONLY TO MC68HC711EA9.

EA9 56-PIN DIP

# Figure 3 MC68HC(7)11EA9 56-Pin SDIP Pin Assignments

6

## 2.2 Ordering Information

The MC68HC(7)11EA9 MCUs are available in a combination of packages, speeds, and temperature ranges. Refer to **Table 1**.

| Description       | Package         | Temperature       | Frequency | MC Order Number  |

|-------------------|-----------------|-------------------|-----------|------------------|

| Buffalo ROM       | 52-Pin PLCC     | - 40° to + 85° C  | 2 MHz     | MC68HC11EA9BCFN2 |

| 12 Kbytes ROM,    |                 |                   | 2 MHz     | MC68HC11EA9CFN2  |

| 512 Bytes RAM     |                 |                   | 3 MHz     | MC68HC11EA9CFN3  |

|                   |                 | - 40° to + 105° C | 2 MHz     | MC68HC11EA9VFN2  |

|                   |                 |                   | 3 MHz     | MC68HC11EA9VFN3  |

|                   |                 | - 40° to + 125° C | 2 MHz     | MC68HC11EA9MFN2  |

|                   |                 |                   | 3 MHz     | MC68HC11EA9MFN3  |

|                   | 56-PIN SDIP     | - 40° to + 85° C  | 2 MHz     | MC68HC11EA9CP2   |

|                   | (.070" Spacing) |                   | 3 MHz     | MC68HC11EA9CP3   |

|                   |                 | - 40° to + 105° C | 2 MHz     | MC68HC11EA9VP2   |

|                   |                 |                   | 3 MHz     | MC68HC11EA9VP3   |

|                   |                 | - 40° to + 125° C | 2 MHz     | MC68HC11EA9MP2   |

|                   |                 |                   | 3 MHz     | MC68HC11EA9MP3   |

| 12 Kbytes OTPROM, | 52-Pin PLCC     | - 40° to + 85° C  | 2 MHz     | MC68HC711EA9CFN2 |

| 512 Bytes RAM     |                 |                   | 3 MHz     | MC68HC711EA9CFN3 |

|                   |                 | - 40° to + 105° C | 2 MHz     | MC68HC711EA9VFN2 |

|                   |                 |                   | 3 MHz     | MC68HC711EA9VFN3 |

|                   |                 | – 40° to + 125° C | 2 MHz     | MC68HC711EA9MFN2 |

|                   |                 |                   | 3 MHz     | MC68HC711EA9MFN3 |

|                   | 56-PIN SDIP     | - 40° to + 85° C  | 2 MHz     | MC68HC711EA9CP2  |

|                   | (.070" Spacing) |                   | 3 MHz     | MC68HC711EA9CP3  |

|                   |                 | – 40° to + 105° C | 2 MHz     | MC68HC711EA9VP2  |

|                   |                 |                   | 3 MHz     | MC68HC711EA9VP3  |

|                   |                 | – 40° to + 125° C | 2 MHz     | MC68HC711EA9MP2  |

|                   |                 |                   | 3 MHz     | MC68HC711EA9MP3  |

| 12 Kbytes EPROM,  | 52-PIN CLCC     | – 40° to + 85° C  | 2 MHz     | MC68HC711EA9CFS2 |

| 512 Bytes RAM     | (Windowed)      |                   | 3 MHz     | MC68HC711EA9CFS3 |

|                   |                 | – 40° to + 105° C | 2 MHz     | MC68HC711EA9VFS2 |

|                   |                 |                   | 3 MHz     | MC68HC711EA9VFS3 |

|                   |                 | – 40° to + 125° C | 2 MHz     | MC68HC711EA9MFS2 |

|                   |                 |                   | 3 MHz     | MC68HC711EA9MFS3 |

### Table 1 Device Ordering Information

# **3 Central Processing Unit**

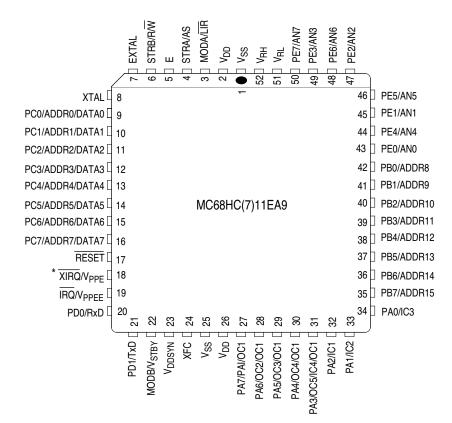

A full description of the CPU and instruction set of M68HC11 MCUs is beyond the scope of this summary. The programming model for the M68HC11 CPU and a brief description of the CPU registers is provided here. For more detailed information refer to the *M68HC11 Reference Manual* (M68HC11RM/AD) or the programming reference guide or technical data book for the appropriate device.

#### 3.1 Programming Model

Figure 4 shows a graphic representation of the internal registers of the M68HC11 CPU.

HC11 PROG MODEL

Figure 4 M68HC11 Programming Model

#### 3.2 CPU Registers

M68HC11 CPU registers are an integral part of the CPU and are not addressed as if they were memory locations. The seven registers, discussed briefly in the following paragraphs, are shown in **Figure 4**. For a complete description of the CPU registers, addressing modes, and instruction set refer to the *M68HC11 Reference Manual* (M68HC11RM/AD).

#### 3.2.1 Accumulators A, B, and D

Accumulators A and B are general-purpose 8-bit registers that hold operands and results of arithmetic calculations or data manipulations. For some instructions, these two accumulators are treated as a single double-byte (16-bit) accumulator called accumulator D. Most instructions can use accumulators A or B interchangeably, however some exceptions apply.

#### 3.2.2 Index Register X (IX)

The IX register provides a 16-bit indexing value that can be added to the 8-bit offset provided in an instruction to create an effective address. The IX register can also be used as a counter or as a temporary storage register.

#### 3.2.3 Index Register Y (IY)

The 16-bit IY register performs an indexed mode function similar to that of the IX register. However, most instructions using the IY register require an extra byte of machine code and an extra cycle of execution time because of the way the opcode map is implemented.

#### 3.2.4 Stack Pointer (SP)

The M68HC11 CPU has an automatic program stack. This stack can be located anywhere in the address space and can be any size up to the amount of memory available in the system. Normally the SP is initialized by one of the first instructions in an application program. The stack is configured as a data structure that grows downward from high memory to low memory. Each time a new byte is pushed onto the stack, the SP is decremented. Each time a byte is pulled from the stack, the SP is incremented. At any given time, the SP holds the 16-bit address of the next free location in the stack.

#### 3.2.5 Program Counter (PC)

The program counter, a 16-bit register, contains the address of the next instruction to be executed. After reset, the program counter is initialized from one of six possible vectors, depending on operating mode and the cause of reset.

#### 3.2.6 Condition Code Register (CCR)

This 8-bit register contains five condition code indicators (C, V, Z, N, and H), two interrupt masking bits, ( $\overline{IRQ}$  and  $\overline{XIRQ}$ ) and a stop disable bit (S). In the M68HC11 CPU, condition codes are automatically updated by most instructions. For example, load accumulator A (LDAA) and store accumulator A (STAA) instructions automatically set or clear the N, Z, and V condition code flags.

#### 3.2.7 Addressing Modes

Six addressing modes can be used to access memory: immediate, direct, extended, indexed, inherent, and relative. These modes are not detailed in this manual. For a complete description of the CPU registers, addressing modes, and instruction set refer to the *M68HC11 Reference Manual* (M68HC11RM/AD).

# 4 Operating Modes and On-Chip Memory

#### 4.1 Single-Chip Mode

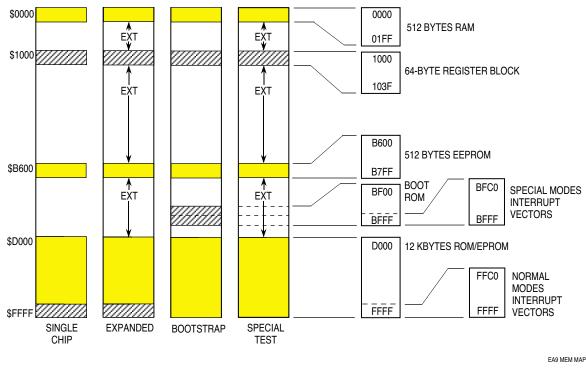

In single-chip mode, ports B and C are available for general-purpose parallel I/O. Strobe pins A (STRA) and B (STRB) can be used to control handshaking of parallel I/O on ports B and C. In this mode, all software needed to control the MCU is contained in internal resources. ROM/EPROM (if present) will always be enabled out of reset, ensuring that the reset and interrupt vectors will be available at locations \$FFC0-\$FFFF.

#### 4.2 Expanded Mode

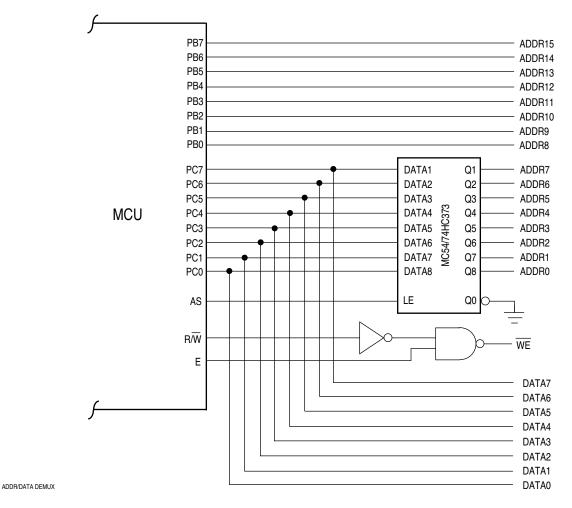

In expanded operating mode, the MCU can access the full 64-Kbyte address space. The space includes the same on-chip memory addresses used for single-chip mode as well as addresses for external peripherals and memory devices. The expansion bus is made up of ports B and C, and control signals AS and R/W. R/W (read/write) and AS (address strobe) allow the low-order address and the 8-bit data bus to be multiplexed on the same pins. During the first half of each bus cycle address information is present. During the second half of each bus cycle the pins become the bidirectional data bus. AS is an active-high latch enable signal for an external address latch. Address information is allowed through the transparent latch while AS is high and is latched when AS drives low. **Figure 5** shows an example of address and data demultiplexing.

#### 4.3 Test Mode

Test mode, a variation of the expanded mode, is primarily used during Motorola's internal production testing; however, it is accessible for programming the CONFIG register, programming calibration data into EEPROM, and supporting emulation and debugging during development. Refer to **Figure 6**.

#### 4.4 Bootstrap Mode

Bootstrap mode is a special variation of the single-chip mode. Bootstrap mode allows special-purpose programs to be entered into internal RAM. When boot mode is selected at reset, a small bootstrap ROM becomes present in the memory map. Reset and interrupt vectors are located in this ROM at \$BFC0-\$BFFF. The bootstrap ROM contains a small program which initializes the SCI and allows the user to download a program into on-chip RAM. The size of the downloaded program can be as large as the size of the on-chip RAM. After a four-character delay, or after receiving the character for the highest address in RAM, control passes to the loaded program at \$0000. Refer to **Figure 6**.

#### 4.5 Mode Selection

The four mode variations are selected by the logic levels present on the MODA and MODB pins during reset. The MODA and MODB logic levels determine the logic state of SMOD and the MDA control bits in the highest priority I-bit interrupt and miscellaneous (HPRIO) register. See **Table 2** for further information.

After reset is released, the mode select pins no longer influence the MCU operating mode. In singlechip operating mode, the MODA pin is connected to a logic level zero. In expanded mode, MODA is normally connected to  $V_{DD}$  through a pull-up resistor of 4.7 k $\Omega$ . The MODA pin also functions as the load instruction register ( $\overline{LIR}$ ) pin when the MCU is not in reset. The  $\overline{LIR}$  signal is useful during program debugging. The open-drain active low  $\overline{LIR}$  output pin drives low during the first E cycle of each instruction. The MODB pin also functions as standby power input ( $V_{STBY}$ ), which allows RAM contents to be maintained in absence of  $V_{DD}$ .

|        | BIT 7  | 6     | 5    | 4     | 3     | 2     | 1     | BIT 0 |

|--------|--------|-------|------|-------|-------|-------|-------|-------|

|        | RBOOT* | SMOD* | MDA* | IRVNE | PSEL3 | PSEL2 | PSEL1 | PSEL0 |

| RESET: | 0      | 0     | 0    | 0     | 0     | 0     | 0     | 0     |

\*The reset values of RBOOT, SMOD, and MDA depend on the mode selected at power up.

#### RBOOT — Read Bootstrap ROM/EPROM

Valid only when SMOD is set (bootstrap or special test mode). Can only be written in special modes.

0 = Bootstrap ROM disabled and not in map

HPRIO — Highest Priority I-bit Interrupt and Miscellaneous

1 = Bootstrap ROM enabled and in map at \$BF00-\$BFFF

#### SMOD and MDA — Special Mode Select and Mode Select A

These two bits can be read at any time. They can be written anytime in special modes. MDA can only be written once in normal modes. SMOD cannot be set once it has been cleared.

| Inputs |      |              | Latched at Rese |      |  |

|--------|------|--------------|-----------------|------|--|

| MODA   | MODB | Mode         | MDA             | SMOD |  |

| 0      | 1    | Single Chip  | 0               | 0    |  |

| 1      | 1    | Expanded     | 1               | 0    |  |

| 0      | 0    | Bootstrap    | 0               | 1    |  |

| 1      | 0    | Special Test | 1               | 1    |  |

\$103C

IRV(NE) — Internal Read Visibility(Not E)

IRVNE can be written once in any mode. In expanded modes, IRVNE determines whether IRV is on or off. In special test mode, IRVNE is reset to one. In all other modes, IRVNE is reset to zero.

0 = No internal read visibility on external bus

1 = Data from internal reads is driven out the external data bus.

In single-chip modes this bit determines whether the E clock drives out from the chip.

0 = E is driven out from the chip.

1 = E pin is driven low. Refer to the following table.

| Operating<br>Mode | IRVNE Bit<br>Out of Reset | E Clock<br>Out of Reset | IRV Function<br>Out of Reset | IRVNE Bit<br>Affects Only |

|-------------------|---------------------------|-------------------------|------------------------------|---------------------------|

| Single Chip       | 0                         | On                      | Off                          | E                         |

| Expanded          | 0                         | On                      | Off                          | IRV                       |

| Bootstrap         | 0                         | On                      | Off                          | E                         |

| Special Test      | 1                         | On                      | On                           | IRV                       |

#### Table 3 IRVNE Control vs. Operating Mode

PSEL[3:0] — Priority Select Bits [3:0]

Refer to 5 Resets and Interrupts

#### 4.6 RAM

In all modes RAM is enabled and present at locations \$0000–\$01FF. The RAM can be mapped to any 1-Kbyte boundary by writing an appropriate value to the INIT register. The INIT register must be written during the first 64 cycles after reset in expanded and single-chip modes. If RAM and the register block are placed at the same 1-Kbyte boundary, the first 64 bytes of RAM are inaccessible. This is due to an on-chip hardware priority scheme which eliminates conflicts which could arise from multiple resources sharing address locations. **Figure 6** shows the location of the RAM array.

#### 4.7 Bootstrap ROM

When operating in normal modes (SMOD = 0), the bootstrap ROM is disabled and removed from the memory map. In bootstrap and special test modes, bootstrap ROM is present at BF00-BFFF. Bootstrap ROM cannot be remapped to other locations. **Figure 6** shows the location of the bootstrap ROM array.

The bootstrap ROM contains a small program that allows program code to be downloaded into on-chip RAM. When the MC68HC(7)11EA9 enters bootstrap mode, bootloader firmware residing in bootstrap ROM begins the downloading procedure by initializing the SCI system and transmitting a break out the SCI TxD pin. The SCI then waits for the first character to be received. After the first character is received on the RxD pin of the SCI, bootloader firmware begins counting the number of bytes received. When an idle time of four characters or the character for address \$01FF is received, the bootloader program terminates the download and control is passed to the loaded program at \$0000. For a detailed description of the M68HC11 bootstrap mode, refer to application note *M68HC11 Bootstrap Mode* (AN1060/D).

#### 4.8 Memory Map and Register Block

The operating mode determines memory mapping and whether external addresses can be accessed. Memory locations for on-chip resources are the same for both expanded and single-chip modes. Control bits in the CONFIG register allow ROM/EPROM and EEPROM to be disabled from the memory map. The RAM is mapped to \$0000 after reset. It can be placed at any 4 Kbyte boundary (\$x000) by writing an appropriate value to the INIT register. The 64-byte register block is mapped to \$1000 after reset and can also be placed at any 4 Kbyte boundary (\$x000) by writing an appropriate value to the INIT register. If RAM and registers are mapped to the same boundary, the first 64 bytes of RAM will be inaccessible. **Table 4** shows the arrangement of control registers and bits within the register block.

Figure 6 MC68HC(7)11EA9 Memory Map

#### INIT - RAM and I/O Mapping Register

|        | BIT 7 | 6    | 5    | 4    | 3    | 2    | 1    | BIT 0 |

|--------|-------|------|------|------|------|------|------|-------|

|        | RAM3  | RAM2 | RAM1 | RAM0 | REG3 | REG2 | REG1 | REG0  |

| RESET: | 0     | 0    | 0    | 0    | 0    | 0    | 0    | 1     |

#### RAM[3:0] - RAM Map Position

These four bits, which specify the upper hexadecimal digit of the RAM address, control position of RAM in the memory map. RAM can be positioned at the beginning of any 4 Kbyte page in the memory map. It is initialized to address \$0000 out of reset.

#### REG[3:0] — 64-Byte Register Block Position

These four bits specify the upper hexadecimal digit of the address for the 64-byte block of internal registers. The register block, positioned at the beginning of any 4 Kbyte page in the memory map, is initialized to address \$1000 out of reset.

\$103D

# Table 4 MC68HC(7)11EA9 Registers (Sheet 1 of 2)

|        |        |       |       | • •   | •      | •     | ,     |       |                |

|--------|--------|-------|-------|-------|--------|-------|-------|-------|----------------|

|        | BIT 7  | 6     | 5     | 4     | 3      | 2     | 1     | BIT 0 |                |

| \$1000 | PA7    | PA6   | PA5   | PA4   | PA3    | PA2   | PA1   | PA0   | PORTA          |

| \$1001 | DDA7   | DDA6  | DDA5  | DDA4  | DDA3   | DDA2  | DDA1  | DDA0  | DDRA           |

| \$1002 | STAF   | STAI  | CWOM  | HNDS  | OIN    | PLS   | EGA   | INVB  | PIOC           |

| \$1003 | PC7    | PC6   | PC5   | PC4   | PC3    | PC2   | PC1   | PC0   | PORTC          |

| \$1004 | PB7    | PB6   | PB5   | PB4   | PB3    | PB2   | PB1   | PB0   | PORTB          |

| \$1005 | PCL7   | PCL6  | PCL5  | PCL4  | PCL3   | PCL2  | PCL1  | PCL0  | PORTCL         |

| \$1006 | DDB7   | DDB6  | DDB5  | DDB4  | DDB3   | DDB2  | DDB1  | DDB0  | DDRB           |

| \$1007 | DDC7   | DDC6  | DDC5  | DDC4  | DDC3   | DDC2  | DDC1  | DDC0  | DDRC           |

| \$1008 | XPIN   | IPIN  | 0     | 0     | 0      | 0     | PD1   | PD0   | PORTD          |

| \$1009 | DISX   | DISI  | 0     | 0     | 0      | 0     | DDD1  | DDD0  | DDRD           |

| \$100A | PE7    | PE6   | PE5   | PE4   | PE3    | PE2   | PE1   | PE0   | PORTE          |

| \$100B | FOC1   | FOC2  | FOC3  | FOC4  | FOC5   | 0     | 0     | 0     | CFORC          |

| \$100C | OC1M7  | OC1M6 | OC1M5 | OC1M4 | OC1M3  | 0     | 0     | 0     | OC1M           |

| \$100D | OC1D7  | OC1D6 | OC1D5 | OC1D4 | OC1D3  | 0     | 0     | 0     | OC1D           |

| \$100E | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TCNT (HI)      |

| \$100F | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TCNT (LO)      |

| \$1010 | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TIC1 (HI)      |

| \$1011 | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TIC1 (LO)      |

| \$1012 | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TIC2 (HI)      |

| \$1013 | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TIC2 (LO)      |

| \$1014 | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TIC3 (HI)      |

| \$1015 | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TIC3 (LO)      |

| \$1016 | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TOC1 (HI)      |

| \$1017 | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TOC1 (LO)      |

| \$1018 | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TOC2 (HI)      |

| \$1019 | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TOC2 (LO)      |

| \$101A | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TOC3 (HI)      |

| \$101B | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TOC3 (LO)      |

| \$101C | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TOC4 (HI)      |

| \$101D | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TOC4 (LO)      |

| \$101E | Bit 15 | 14    | 13    | 12    | 11     | 10    | 9     | Bit 8 | TI4/O5 (HI)    |

| \$101F | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | TI4/O5<br>(LO) |

| \$1020 | OM2    | OL2   | OM3   | OL3   | OM4    | OL4   | OM5   | OL5   | TCTL1          |

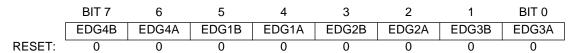

| \$1021 | EDG4B  | EDG4A | EDG1B | EDG1A | EDG2B  | EDG2A | EDG3B | EDG3A | TCTL2          |

| \$1022 | OC1I   | OC2I  | OC3I  | OC4I  | I4/O5I | IC1I  | IC2I  | IC3I  | TMSK1          |

| \$1023 | OC1F   | OC2F  | OC3F  | OC4F  | 14/05F | IC1F  | IC2F  | IC3F  | TFLG1          |

| \$1024 | TOI    | RTII  | PAOVI | PAII  | 0      | 0     | PR1   | PR0   | TMSK2          |

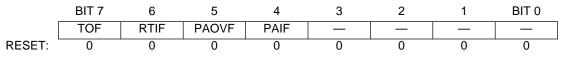

| \$1025 | TOF    | RTIF  | PAOVF | PAIF  | 0      | 0     | 0     | 0     | TFLG2          |

| \$1026 | 0      | PAEN  | PAMOD | PEDGE | 0      | I4/05 | RTR1  | RTR0  | PACTL          |

| \$1027 | Bit 7  | 6     | 5     | 4     | 3      | 2     | 1     | Bit 0 | PACNT          |

| \$1028 | BTST   | BSPL  | BRST  | SBR12 | SBR11  | SBR10 | SBR9  | SBR8  | SCBDH          |

| \$1029 | SBR7   | SBR6  | SBR5  | SBR4  | SBR3   | SBR2  | SBR1  | SBR0  | SCBDL          |

| \$102A | LOOPS  | WOMS  | 0     | М     | WAKE   | ILT   | PE    | PT    | SCCR1          |

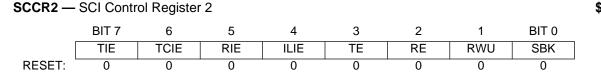

| \$102B | TIE    | TCIE  | RIE   | ILIE  | TE     | RE    | RWU   | SBK   | SCCR2          |

| \$102C | TDRE   | TC    | RDRF  | IDLE  | OR     | NF    | FE    | PF    | SCSR1          |

| \$102D | 0      | 0     | 0     | 0     | 0      | 0     | 0     | RAF   | SCSR2          |

| \$102E | R8     | T8    | 0     | 0     | 0      | 0     | 0     | 0     | SCDRH          |

|        |        |       |       |       |        |       |       |       |                |

|        | BIT 7 | 6     | 5                 | 4     | 3     | 2     | 1     | BIT 0 |                    |

|--------|-------|-------|-------------------|-------|-------|-------|-------|-------|--------------------|

| \$102F | R7/T7 | R6/T6 | R5/T5             | R4/T4 | R3/T3 | R2/T2 | R1/T1 | R0/T0 | SCDRL              |

| \$1030 | CCF   | 0     | SCAN              | MULT  | CD    | CC    | СВ    | CA    | ADCTL              |

| \$1031 | Bit 7 | 6     | 5                 | 4     | 3     | 2     | 1     | Bit 0 | ADR1               |

| \$1032 | Bit 7 | 6     | 5                 | 4     | 3     | 2     | 1     | Bit 0 | ADR2               |

| \$1033 | Bit 7 | 6     | 5                 | 4     | 3     | 2     | 1     | Bit 0 | ADR3               |

| \$1034 | Bit 7 | 6     | 5                 | 4     | 3     | 2     | 1     | Bit 0 | ADR4               |

| \$1035 | 0     | 0     | 0                 | PTCON | BPRT3 | BPRT2 | BPRT1 | BPRT0 | BPROT              |

| \$1036 | PLLON | BCS   | AUTO              | BWC   | VCOT  | MCS   | LCK   | WEN   | PLLCR              |

| \$1037 | SYNX1 | SYNX0 | SYNY5             | SYNY4 | SYNY3 | SYNY2 | SYNY1 | SYNY0 | SYNR               |

| \$1038 |       |       |                   |       |       |       |       |       | Reserved           |

| \$1039 | ADPU  | CSEL  | IRQE              | DLY   | CME   | 0     | CR1   | CR0   | OPTION             |

| \$103A | Bit 7 | 6     | 5                 | 4     | 3     | 2     | 1     | Bit 0 | COPRST             |

| \$103B | ODD   | EVEN  | ELAT <sup>1</sup> | BYTE  | ROW   | ERASE | EELAT | PGM   | PPROG              |

| \$103C | RBOOT | SMOD  | MDA               | IRVNE | PSEL3 | PSEL2 | PSEL1 | PSEL0 | HPRIO              |

| \$103D | RAM3  | RAM2  | RAM1              | RAM0  | REG3  | REG2  | REG1  | REG0  | INIT               |

| \$103E | —     | —     | —                 | —     | —     | —     | —     | —     | TEST1 <sup>2</sup> |

| \$103F | 0     | 0     | 0                 | 0     | NOSEC | NOCOP | ROMON | EEON  | CONFIG             |

| Nataa. |       |       |                   |       |       |       |       |       |                    |

#### Table 4 MC68HC(7)11EA9 Registers (Sheet 2 of 2)

Notes:

1. MC68HC711EA9 only.

2. Factory test only.

#### 4.9 ROM/EPROM/OTPROM

The MC68HC11EA9 contains 12 Kbytes of mask-programmed ROM. The ROM array is programmed at the factory to customer specifications and cannot be altered. The ROM array can be disabled by clearing the ROMON bit in the CONFIG register.

The MC68HC711EA9 MCU contains 12 Kbytes of on-chip EPROM/OTPROM. When the MC68HC711EA9 is packaged in a windowed CLCC, the 12 Kbytes of EPROM may be erased by exposing the device to ultraviolet light. An MC68HC711EA9 MCU packaged in a non-windowed case contains 12 Kbytes of one-time-programmable ROM (OTPROM).

Using the on-chip EPROM/OTPROM programming feature requires an external 12.25-volt power supply ( $V_{PPE}$ ). Normal programming is accomplished using the EPROM/OTPROM programming register (PPROG). PPROG is the combined EPROM/OTPROM and EEPROM programming register (MC68HC711EA9 only). For the MC68HC11EA9, PPROG is used for programming EEPROM only. There are three possible methods of programming and verifying EPROM.

#### 4.9.1 EPROM Emulation Mode

The EPROM emulation (PROG) mode allows the on-chip EPROM/OTPROM to be programmed as a standard EPROM by adapting the MCU footprint to that of the 27256-type EPROM, as shown in **Figure 7**. Grounding the RESET, MODA, and MODB pins places the MCU in PROG mode. An appropriate EPROM programmer can then be used to enter data into the on-chip EPROM. **Figure 7** shows the MCU pin functions while the device is in PROG mode.

If the MCU is operating with programming voltage present on the  $\overline{XIRQ}/V_{PPE}$  pin, the  $\overline{IRQ}$  pin ( $\overline{CE}$  pin in PROG mode) must be pulled high before the address and data are changed to program the next location.

#### NOTE

PROG mode is disabled in devices having the security feature.

|        | A1 PC<br>A2 PC<br>A3 PC<br>A3 PC<br>A4 PC<br>A5 PC<br>A6 PC | 0/ADDR0/DATA0<br>1/ADDR1/DATA1<br>2/ADDR2/DATA2<br>3/ADDR3/DATA3<br>4/ADDR4/DATA4<br>5/ADDR5/DATA5<br>6/ADDR6/DATA6<br>7/ADDR7/DATA7<br>PB0/ADDR8<br>PB1/ADDR9<br>PB2/ADDR10<br>PB3/ADDR11<br>PB3/ADDR11<br>PB4/ADDR12<br>PB5/ADDR13<br>NC | A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7<br>A8<br>A9<br>A10<br>A11<br>A12<br>A13 | INTERNAL<br>12-KBYTE<br>EPROM | 00<br>01<br>02<br>03<br>04<br>05<br>06<br>07<br>0Е<br>V <sub>PP</sub><br><u>CE</u><br>V <sub>CC</sub><br>GND | PD0/RxD<br>PD1/TxD<br>PA2/IC1<br>PA3/OC5/IC4/OC1<br>PA4/OC4/OC1<br>PA5/OC3/OC1<br>STRA/AS<br>STRB/R/W<br>PB7/ADDR15<br>XIRQ<br>IRQ<br>V <sub>DD</sub><br>V <sub>SS</sub> | 00<br>01<br>02<br>03<br>04<br>05<br>06<br>07<br>0E<br>V <sub>PP</sub><br>CE<br>V <sub>CC</sub><br>GND |        |

|--------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|--------|

|        | GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND        | PE0/AN0<br>PE1/AN1<br>PE2/AN2<br>PE3/AN3<br>PE4/AN4<br>PE5/AN5<br>PE6/AN6<br>PE7/AN7                                                                                                                                                       | MC68HC711EA9                                                                         |                               |                                                                                                              | PA4/OC4/OC1<br>PA5/OC3/OC1<br>XTAL<br>E                                                                                                                                  | NC<br>NC<br>NC                                                                                        | NOTE 2 |

| NOTE 1 | GND<br>GND<br>GND<br>GND<br>GND<br>MD                       | PA6/OC2/OC1<br>PA7/PAI/OC1<br>V <sub>RH</sub><br>V <sub>RL</sub><br>V <sub>DDSYN</sub><br>XFC                                                                                                                                              |                                                                                      |                               |                                                                                                              | EXTAL<br>MODA/LIR<br>MODB/V <sub>STBY</sub><br>RESET<br>PB6/ADDR14<br>PA0/IC3<br>PA1/IC2                                                                                 | GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND<br>GND                                                  | NOTE 3 |

NOTES:

1. UNUSED INPUTS — GROUNDING IS RECOMMENDED.

2. UNUSED OUTPUTS — THESE PINS SHOULD BE LEFT UNTERMINATED.

3. THESE PINS MUST BE GROUNDED FOR PROG MODE OPERATION.

7EA9 PROG CONN

#### Figure 7 MC68HC711EA9 PROG Mode Connections

#### 4.9.2 Programming an Individual EPROM Address

In the second method, the MCU programs its own EPROM by controlling the PPROG register. Use the following procedure to program the EPROM through the MCU with the ROMON bit set in the CONFIG register. The 12 volt nominal programming voltage must be present on the  $\overline{XIRQ}/V_{PPE}$  pin. Any operating mode can be used.

- 1. Write to PPROG to set the ELAT bit.

- 2. Write the data to the desired address.

- 3. Write to PPROG to set both the ELAT and PGM bits.

- 4. Delay for 10 ms or more, as appropriate.

- 5. Clear the PGM bit to turn off the  $V_{PPE}$  voltage.

- 6. Clear all bits in the PPROG register to reconfigure the EPROM address and data buses for normal operation.

#### NOTE

PROG mode is initiated when RESET, MODA, and MODB pins are pulled low (the pin state required to enter bootstrap mode). This means that if these three pins are pulled low and V<sub>PPE</sub> is present on the XIRQ pin, the EPROM will be programmed. To prevent this, place a pull-up resistor on the IRQ pin ( $\overline{CE}$  pin in PROG mode). When the device goes into reset, the PGM bit is forced to the voltage disable state (EPGM = 0) before the address/data latches are enabled to the external input lines. Only after this occurs is voltage control returned to the IRQ pin.

#### 4.9.3 Programming EPROM with Downloaded Data

When using this method, the EPROM is programmed by software while in the special test or bootstrap modes. User-developed software can be uploaded through the SCI, or a ROM resident EPROM programming utility can be used. To use the resident utility, bootload a three-byte program consisting of a single jump instruction to \$BF00. \$BF00 is the starting address of a resident EPROM programming utility. The utility program sets the X and Y index registers to default values, then receives programming data from an external host and puts it in EPROM. The value in IX determines programming delay time. The value in IY is a pointer to the first address in EPROM to be programmed (default = \$D000).

When the utility program is ready to receive programming data, it sends the host the \$FF character. Then it waits. When the host sees the \$FF character, the EPROM programming data is sent, starting with the first location in the EPROM array. After the last byte to be programmed is sent and the corresponding verification data is returned, the programming operation is terminated by resetting the MCU.

| PPROG — | <ul> <li>— EPROM and EEPROM Programming Control Register</li> </ul> |      |       |      |     |       | \$103B |       |  |

|---------|---------------------------------------------------------------------|------|-------|------|-----|-------|--------|-------|--|

|         | BIT 7                                                               | 6    | 5     | 4    | 3   | 2     | 1      | BIT 0 |  |

|         | ODD                                                                 | EVEN | ELAT* | BYTE | ROW | ERASE | EELAT  | PGM   |  |

| RESET:  | 0                                                                   | 0    | 0     | 0    | 0   | 0     | 0      | 1     |  |

\* MC68HC711EA9 only.

ODD — Program Odd Rows in Half of EEPROM (TEST) Refer to **4.10 EEPROM**.

EVEN — Program Even Rows in Half of EEPROM (TEST) Refer to **4.10 EEPROM**.

#### ELAT — EPROM/OTPROM Latch Control

When ELAT = 1, writes to EPROM cause address and data to be latched and the EPROM/OTPROM cannot be read. ELAT can be read any time. ELAT can be written any time except when EPGM = 1; then the write to ELAT is disabled. For MC68HC711EA9, EPGM enables the high voltage necessary for both EPROM/OTPROM and EEPROM programming. For MC68HC711EA9 ELAT and EELAT are mutually exclusive and cannot both equal one.

- 0 = EPROM address and data bus configured for normal reads

- 1 = EPROM address and data bus configured for programming

- BYTE Byte/Other EEPROM Erase Mode Refer to **4.10 EEPROM**.

- ROW Row/All EEPROM Erase Mode Refer to **4.10 EEPROM**.

ERASE — Erase/Normal Control for EEPROM Refer to **4.10 EEPROM**.

EELAT — EEPROM Latch Control

- 0 = EEPROM address and data bus configured for normal reads

- 1 = EEPROM address and data bus configured for programming or erasing

PGM — EPROM/OTPROM/EEPROM Programming Voltage Enable

0 = Programming voltage to EPROM/OTPROM/EEPROM array disconnected

1 = Programming voltage to EPROM/OTPROM/EEPROM array connected

PGM can be read any time and can only be written when ELAT = 1 (for EPROM/OTPROM programming) or when EELAT = 1 (for EEPROM programming).

#### 4.10 EEPROM

MC68HC(7)11EA9 MCUs contain 512 bytes of EEPROM. The 512-byte EEPROM is initially located at \$B600 after reset, assuming EEPROM is enabled in the memory map by the EEON bit in the CONFIG register. EEPROM can be placed at any 4 Kbyte boundary (\$x600) by writing appropriate values to the INIT register. Note that EEPROM can be mapped such that it contains the vector space. See **Figure 6**.

#### 4.10.1 Programming and Erasing EEPROM

Programming and erasing the EEPROM is controlled by the PPROG register, and is dependent upon the block protect (BPROT) register value. The erased state of an EEPROM bit is one. During a read operation, bit lines are precharged to one. The floating gate devices of programmed bits conduct and pull the bit lines to zero. Unprogrammed bits remain at the precharged level and are read as ones. Programming a bit to one causes no change. Programming a bit to zero changes the bit so that subsequent reads return zero.

When appropriate bits in the BPROT register are cleared, the PPROG register controls programming and erasing of the EEPROM. The PPROG register can be read or written at any time, but logic enforces defined programming and erasing sequences to prevent unintentional changes to data in EEPROM. When the EELAT bit in the PPROG register is cleared, the EEPROM can be read as if it were a ROM.

The on-chip charge pump that generates the EEPROM programming voltage from  $V_{DD}$  uses MOS capacitors, which are relatively small in value. The efficiency of this charge pump and its drive capability are affected by the level of  $V_{DD}$  and the frequency of the driving clock. The clock source driving the charge pump is software selectable. When the clock select (CSEL) bit in the OPTION register is zero, the E clock is used; when CSEL is one, an on-chip resistor-capacitor (RC) oscillator is used. The RC oscillator should be used when E < 1 MHz. This RC oscillator will drive the A/D circuitry as well as the EEPROM charge pump when CSEL = 1.

The EEPROM programming voltage connection to the EEPROM array is not enabled until there has been a write to PPROG with EELAT set and PGM cleared. This must be followed by a write to a valid EEPROM location or to the CONFIG address, and then a write to PPROG with both EELAT and PGM set. Any attempt to set both EELAT and PGM during the same write operation results in neither bit being set.

The erased state of an EEPROM byte is \$FF (all ones).

To erase the EEPROM, ensure that the proper bits of the BPROT register are cleared, then complete the following steps using the PPROG register:

- 1. Set the ERASE, EELAT, and appropriate BYTE and ROW bits in PPROG register.

- 2. Write to the appropriate EEPROM address with any data. Row erase only requires a write to any location in the row. Bulk erase is done by writing to any location in the array.

- 3. Set the ERASE, EELAT, EEPGM, and appropriate BYTE and ROW bits in PPROG register.

- 4. Delay for 10 ms or more, as appropriate.

- 5. Clear the EEPGM bit in PPROG to turn off the programming voltage.

- 6. Clear the PPROG register to reconfigure the EEPROM address and data buses for normal operation.

To program the EEPROM, ensure the proper bits of the BPROT register are cleared and use the PROG register to complete the following steps:

- 1. Set the EELAT bit in PPROG register.

- 2. Write data to the desired address.

- 3. Set EEPGM bit in PPROG.

- 4. Delay for 10 ms or more, as appropriate.

- 5. Clear the EEPGM bit in PPROG to turn off the programming voltage.

- Clear the PPROG register to reconfigure the EEPROM address and data buses for normal operation.

#### CAUTION

Since it is possible to perform other operations while the EEPROM programming/ erase operation is in progress, it is common to start the operation then return to the main program until the 10 ms is completed. When the EELAT bit is set at the beginning of a program/erase operation, the EEPROM is electronically removed from the memory map; thus, it is not accessible during the program/erase cycle. Care must be taken to ensure that EEPROM resources will not be needed by any routines in the code during the 10 ms program/erase time.

**BPROT** — EEPROM Block Protect

\$1035

|        | BIT 7 | 6 | 5 | 4     | 3     | 2     | 1     | BIT 0 |

|--------|-------|---|---|-------|-------|-------|-------|-------|

|        | _     | — |   | PTCON | BPRT3 | BPRT2 | BPRT1 | BPRT0 |

| RESET: | 0     | 0 | 0 | 1     | 1     | 1     | 1     | 1     |

Active bits in BPROT reset to ones in all modes and can only be cleared during the first 64 cycles out of reset. Bits can be set only once in normal modes. In special modes, bits can be set and cleared repeatedly.

Bits [7:5] — Not implemented

Always read zero

#### PTCON — Protect CONFIG Register

- 0 = CONFIG register can be programmed or erased normally

- 1 = CONFIG register cannot be programmed or erased

#### BPRT[3:0] — Block Protect Bits for EEPROM

When set, these bits protect a block of EEPROM from being programmed or electronically erased. Ultraviolet light, however can erase the entire EEPROM contents regardless of BPRT[3:0] (windowed packages only). When cleared, they allow programming and erasure of the associated block.

#### **Table 5 EEPROM Block Protect**

| Bit Name | Block Protected | Block Size |

|----------|-----------------|------------|

| BPRT0    | \$B600-\$B61F   | 32 Bytes   |

| BPRT1    | \$B620-\$B65F   | 64 Bytes   |

| BPRT2    | \$B660-\$B6DF   | 128 Bytes  |

| BPRT3    | \$B6E0-\$B7FF   | 288 Bytes  |

**PPROG** — EPROM and EEPROM Programming Control Register

\$103B

|        | BIT 7 | 6    | 5     | 4    | 3   | 2     | 1     | BIT 0 |  |

|--------|-------|------|-------|------|-----|-------|-------|-------|--|

|        | ODD   | EVEN | ELAT* | BYTE | ROW | ERASE | EELAT | PGM   |  |

| RESET: | 0     | 0    | 0     | 0    | 0   | 0     | 0     | 1     |  |

\* MC68HC711EA9 only.

- ODD Program Odd Rows in Half of EEPROM (TEST)

- EVEN Program Even Rows in Half of EEPROM (TEST)

- ELAT EPROM/OTPROM Latch Control

MC68HC711EA9 only. Refer to **4.9.3 Programming EPROM with Downloaded Data**.

- BYTE Byte/Other EEPROM Erase Mode

- 0 = Row or bulk erase mode used

- 1 = Erase only one byte of EEPROM

- ROW Row/All EEPROM Erase Mode (only valid when BYTE = 0)

- 0 = All 512 bytes of EEPROM erased

- 1 = Erase only one 16-byte row of EEPROM

#### Table 6 BYTE/ROW Control Bits

| BYTE | ROW | Action                     |

|------|-----|----------------------------|

| 0    | 0   | Bulk Erase (All 512 Bytes) |

| 0    | 1   | Row Erase (16 Bytes)       |

| 1    | 0   | Byte Erase                 |

| 1    | 1   | Byte Erase                 |

ERASE — Erase/Normal Control for EEPROM

- 0 = Normal read or program mode

- 1 = Erase mode

- EELAT EEPROM Latch Control

- 0 = EEPROM address and data bus configured for normal reads

- 1 = EEPROM address and data bus configured for programming or erasing

PGM — EPROM/OTPROM/EEPROM Programming Voltage Enable

0 = Programming voltage to EPROM/OTPROM/EEPROM array disconnected

1 = Programming voltage to EPROM/OTPROM/EEPROM array connected

PGM can be read any time and can only be written when ELAT = 1 (for EPROM/OTPROM programming) or when EELAT = 1 (for EEPROM programming).

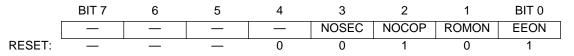

#### 4.10.2 CONFIG Register

The CONFIG register consists of an EEPROM byte and static latches that control the start-up configuration of the MCU. The contents of the EEPROM byte are transferred into static working latches during reset sequences. The operation of the MCU is controlled directly by these latches and not by CONFIG itself. Although the byte is not included in the 512-byte EEPROM array, programming the CONFIG register requires the same procedure as any byte in the array. In normal modes, changes to CONFIG do not affect operation of the MCU until after the next reset sequence. When programming, the CONFIG register itself is accessed. When the CONFIG register is read, the static latches are accessed.

#### **CONFIG** — Security, COP, ROM/EPROM, and EEPROM Enables

|          | BIT 7 | 6 | 5 | 4 | 3     | 2     | 1     | BIT 0 |

|----------|-------|---|---|---|-------|-------|-------|-------|

|          | _     | _ | _ | — | NOSEC | NOCOP | ROMON | EEON  |

| RESETS:  |       |   |   |   |       |       |       |       |

| S. Chip: | 0     | 0 | 0 | 0 | U     | U     | 1     | U     |

| Boot:    | 0     | 0 | 0 | 0 | U     | U(L)  | U     | U     |

| Exp.:    | 0     | 0 | 0 | 0 | 1     | U     | U     | U     |

| Test:    | 0     | 0 | 0 | 0 | 1     | U(L)  | U     | U     |

U indicates a previously programmed bit. U(L) indicates that the bit resets to the logic level held in the latch prior to reset (unchanged), but the function of COP is controlled by DISR bit in TEST1 register.

#### Bits [7:4] - Not Implemented

Always read zero

#### NOSEC — Security Disable

NOSEC is invalid unless the security mask option is specified before the MCU is manufactured. If security mask option is omitted NOSEC always reads one. The security feature protects the contents of RAM and EEPROM.

0 = Security enabled

1 = Security disabled

NOCOP — COP System Disable

#### Refer to 5 Resets and Interrupts.

#### ROMON — ROM/EPROM/OTPROM Enable

When this bit is zero, the ROM or EPROM/OTPROM is disabled and that memory space becomes externally addressed. In single-chip mode, ROMON is forced to one to enable ROM/EPROM/OTPROM regardless of the state of the ROMON bit.

0 = ROM/EPROM/OTPROM disabled from the memory map

1 = ROM/EPROM/OTPROM present in the memory map

#### EEON — EEPROM Enable

When this bit is zero, the EEPROM is disabled and that memory space becomes externally addressed.

0 = EEPROM removed from the memory map

1 = EEPROM present in the memory map

#### 4.10.3 EEPROM Security

The optional security feature, available only on ROM-based MCUs, protects the EEPROM and RAM contents from unauthorized access. A program, or a key portion of a program, can be protected against unauthorized duplication. To accomplish this, the protection mechanism restricts operation of protected devices to the single-chip modes. This prevents the memory locations from being monitored externally because single-chip modes do not allow visibility of the internal address and data buses. Resident programs, however, have unlimited access to the internal EEPROM and RAM and can read, write, or transfer the contents of these memories.

## **5 Resets and Interrupts**

All M68HC11 MCUs have three reset vectors and 18 interrupt vectors. The reset vectors are as follows:

- RESET, or Power-On Reset

- Clock Monitor Fail

- COP Failure

The 18 interrupt vectors service 22 interrupt sources (3 non-maskable, 19 maskable). The 3 non-maskable interrupt sources are as follows:

- Illegal Opcode Trap

- Software Interrupt

- XIRQ Pin (X Interrupt)

On-chip peripheral systems generate maskable interrupts, which are recognized only if the global interrupt mask bit (I) in the condition code register (CCR) is clear. Maskable interrupts are prioritized according to a default arrangement; however, any one source can be elevated to the highest maskable priority position by a software-accessible control register (HPRIO). The HPRIO register can be written at any time, provided bit I in the CCR is set.

Eighteen interrupt sources in the MC68HC(7)11EA9 MCUs are subject to masking by the global interrupt mask bit (bit I in the CCR). In addition to the global bit I, all of these sources, except the external interrupt (IRQ) pin, are controlled by local enable bits in control registers. Most interrupt sources in the M68HC11 have separate interrupt vectors; therefore, there is usually no need for software to poll control registers to determine the cause of an interrupt.

For some interrupt sources, such as the SCI interrupts, the flags are automatically cleared during the normal course of responding to the interrupt requests. For example, the RDRF flag in the SCI system is cleared by the automatic clearing mechanism invoked by a read of the SCI status register while RDRF is set, followed by a read of the SCI data register. The normal response to an RDRF interrupt request would be to read the SCI status register to check for receive errors, then to read the received data from the SCI data register. These two steps satisfy the automatic clearing mechanism without requiring any special instructions.

The computer operating properly (COP) watchdog and the clock monitor are both circuits that force a reset sequence when a malfunctioning clock is encountered. The COP function forces a reset when a timeout occurs. The timeout period is determined by programming CR[1:0] in OPTION register. The clock monitor circuit forces a reset sequence whenever the clock is slow or absent. The CME bit in the OPTION register enables the clock monitor circuit. To use STOP mode the clock monitor must be disabled before the STOP instruction is executed or a reset sequence will occur.

Refer to the following table for a list of interrupt and reset vector assignments.

| -                                |                                                                                                                                                                                        |                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                          |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Interrupt Source                 | CCR Mask                                                                                                                                                                               | Local Mask                                                                                                                                                                                                                 | Priority<br>(1 = High)                                                                                                                                                                                                                                                   |

| Reserved                         | —                                                                                                                                                                                      | _                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                          |

| SCI Serial System                | Bit I                                                                                                                                                                                  |                                                                                                                                                                                                                            | 18                                                                                                                                                                                                                                                                       |

| SCI Receive Data Register Full   |                                                                                                                                                                                        | RIE                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                          |

| SCI Receiver Overrun             |                                                                                                                                                                                        | RIE                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                          |

| SCI Transmit Data Register Empty |                                                                                                                                                                                        | TIE                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                          |

| SCI Transmit Complete            |                                                                                                                                                                                        | TCIE                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                          |

| SCI Idle Line Detect             |                                                                                                                                                                                        | ILIE                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                          |

| Reserved                         | —                                                                                                                                                                                      | _                                                                                                                                                                                                                          | —                                                                                                                                                                                                                                                                        |

|                                  | Reserved<br>SCI Serial System<br>• SCI Receive Data Register Full<br>• SCI Receiver Overrun<br>• SCI Transmit Data Register Empty<br>• SCI Transmit Complete<br>• SCI Idle Line Detect | Reserved     —       SCI Serial System     Bit I       • SCI Receive Data Register Full     Bit I       • SCI Receiver Overrun     SCI Transmit Data Register Empty       • SCI Transmit Complete     SCI Idle Line Detect | Reserved     —     —       SCI Serial System     Bit I       • SCI Receive Data Register Full     RIE       • SCI Receiver Overrun     RIE       • SCI Transmit Data Register Empty     TIE       • SCI Transmit Complete     TCIE       • SCI Idle Line Detect     ILIE |

| <b>Table 7 Interrupt and Reset</b> | Vector Assignments |

|------------------------------------|--------------------|

|------------------------------------|--------------------|

| Pulse Accumulator Input Edge           | Rit I                                                                                                                                                                                                                                                                                                                                                                                                                                      | ΡΔΙΙ                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Pulse Accumulator Overflow             | Bit I                                                                                                                                                                                                                                                                                                                                                                                                                                      | PAOVI                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Timer Overflow                         | Bit I                                                                                                                                                                                                                                                                                                                                                                                                                                      | TOI                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Timer Input Capture 4/Output Compare 5 | Bit I                                                                                                                                                                                                                                                                                                                                                                                                                                      | I4/05I                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |